olimex:lime_gpio

Table des matières

GPIO de l'Olimex LIME A10

La réf: https://github.com/OLIMEX/OLINUXINO/blob/master/HARDWARE/A10-OLinuXino-LIME/A10_Lime_GPIOs.pdf

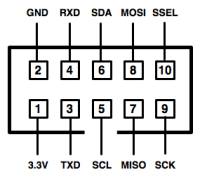

LIME-UEXT L'extension pratique

| 3.3 V | 1 - 2 | GND |

| PG10/UART4_TX GPIO 1-25 | 3 - 4 | LCD_D6(PG11/UART4_RX) GPIO 1-27 |

| PB20/TWI2 SCK SCLGPIO 1-32 | 5 - 6 | PB21/TWI2SDA) GPIO 1-30 |

| TPY1 PC22/SPI2_MISO) GPIO 1-39 | 7 - 8 | TPX1 PC21/SPI2_MOSI GPIO-37 |

| PC20 SPI2_CLK)(PI13) GPIO 1-35 | 9 -10 | L/R(PC19/SPI2_SC0)GPIO 1-33 |

| Pin | Signal Name |

| 1 | 3.3V |

| 2 | GND |

| 3 | TXD |

| 4 | RXD |

| 5 | SCL |

| 6 | SDA |

| 7 | MISO |

| 8 | MOSI |

| 9 | SCK |

| 10 | SSEL |

GND 2 4 6 8 10 ___________ | : : : : : | ----- ----- 1 3 5 7 9 +3,3

GPIO-1

| FUNCTIONS | SIGNAL NAME | PIN | PIN | SIGNAL NAME | FUNCTIONS | |

| . | GND | 2 | 1 | 5V | . | |

| . | AGND | 4 | 3 | 3.3V | . | |

| LRADC0 | LRADC0 | 6 | 5 | PG0 | TS1_CLK/CSI1_PCLK/SDC1_CMD/PG0 | |

| LRADC1 | LRADC1 | 8 | 7 | PG1 | TS1_ERR/CSI1_MLCK/SDC1_CLK/PG1 | |

| MICIN1 | MICIN1 | 10 | 9 | PG2 | TS1_SYNC/CSI1_HSYNC/SDC1_D0/PG2 | |

| VMIC | VMIC | 12 | 11 | PG3 | TS1_DVLD/CSI1_VSYNC/SDC1_D1/PG3 | |

| HPOUTL | HPOUTL | 14 | 13 | PG4 | TS1_D0/CSI1_D0/SDC1_D2/CSI0_D8/PG4 | |

| HPCOM | HPCOM | 16 | 15 | PG5 | TS1_D1/CSI1_D1/SDC1_D3/CSI0_D9/PG5 | |

| HPOUTR | HPOUTR | 18 | 17 | PG6 | TS1_D2/CSI1_D2/UART3_TX/CSI0_D10/PG6 | |

| TVOUT0/VGA-G | VGA-G | 20 | 19 | PG7 | TS1_D3/CSI1_D3/UART3_RX/CSI0_D11/PG7 | |

| TVOUT1/VGA-B | VGA-B | 22 | 21 | PG8 | TS1_D4/CSI1_D4/UART3_RTS/CSI0_D12/PG8 | |

| TVOUT2/VGA-R | VGA-R | 24 | 23 | PG9 | TS1_D5/CSI1_D5/UART3_CTS/CSI0_D13/PG9 | |

| UART0_TX/IR1_TX/PB22 | UART0-RX | 26 | 25 | PG10 | TS1_D6/CSI1_D6/UART4_TX/CSI0_D14/PG10 | |

| UART0_RX/IR1_RX/PB23 | UART0-TX | 28 | 27 | PG11 | TS1_D7/CSI1_D7/UART4_RX/CSI0_D15/PG11 | |

| TWI2_SDA/PB21 | PB21 | 30 | 29 | PC3 or SATA-PWR-EN | NCE1/PC3 or NC | |

| TWI2_SCK/PB20 | PB20 | 32 | 31 | PC18 | NCE3/PC18 | |

| TWI1_SDA/PB19 | PB19 | 34 | 33 | PC19 | NCE4/SPI2_CS0/PC19 | |

| TWI1_SCK/PB18 | PB18 | 36 | 35 | PC20 | NCE5/SPI2_CLK/PC20 | |

| NDQS/PC24 | PC24 | 38 | 37 | PC21 | NCE6/SPI2_MOSI/PC21 | |

| SPI0_CS0/PC23 | PC23 | 40 | 39 | PC22 | NCE7/SPI2_MISO/PC22 | |

en explorant le script.bin avec bin2fex , outil de sunxi-tools, on a :

- UART0 active pin 1-26 RX et 1-28 TX

[uart_para0] uart_used = 1 uart_port = 0 uart_type = 2 uart_tx = port:PB22<2><1><default><default> uart_rx = port:PB23<2><1><default><default>

- UART 4 active pin 1-25 TX et 1-27 RX et sur UEXT 3=TX 4=RX

[uart_para4] uart_used = 1 uart_port = 4 uart_type = 2 uart_tx = port:PG10<4><1><default><default> uart_rx = port:PG11<4><1><default><default>

- I2C 1

[twi1_para] twi1_used = 1 twi1_scl = port:PB18<2><default><default><default> twi1_sda = port:PB19<2><default><default><default>

- I2C 2

[twi2_para] twi2_used = 1 twi2_scl = port:PB20<2><default><default><default> twi2_sda = port:PB21<2><default><default><default>

Olimex spi

modif du .config pour le noyo

CONFIG_SPI=y CONFIG_SPI_MASTER=y CONFIG_SPI_SUN4I=y CONFIG_SPI_SPIDEV=y

Modifier le script.txt ( fex2bin script.txt script.bin )

[spi0_para] spi_used = 0 spi_cs_bitmap = 1 spi_cs0 = port:PI10<3><default><default><default> spi_sclk = port:PI11<3><default><default><default> spi_mosi = port:PI12<3><default><default><default> spi_miso = port:PI13<3><default><default><default> [spi1_para] spi_used = 0 spi_cs_bitmap = 1 spi_cs0 = port:PA00<4><default><default><default> spi_sclk = port:PA01<4><default><default><default> spi_mosi = port:PA02<4><default><default><default> spi_miso = port:PA03<4><default><default><default> [spi2_para] spi_used = 1 spi_cs_bitmap = 1 #spi_cs0 = port:PB14<2><default><default><default> #spi_sclk = port:PB15<2><default><default><default> #spi_mosi = port:PB16<2><default><default><default> #spi_miso = port:PB17<2><default><default><default> spi_cs0 = port:PC19<3><default><default><default> spi_sclk = port:PC20<3><default><default><default> spi_mosi = port:PC21<3><default><default><default> spi_miso = port:PC22<3><default><default><default> [spi3_para] spi_used = 0 spi_cs_bitmap = 1 spi_cs0 = port:PA05<3><default><default><default> spi_sclk = port:PI06<3><default><default><default> spi_mosi = port:PI07<3><default><default><default> spi_miso = port:PI08<3><default><default><default> spi_cs1 = port:PA09<3><default><default><default> [spi_devices] spi_dev_num = 1 [spi_board0] modalias = "spidev" max_speed_hz = 12000000 bus_num = 2 chip_select = 0 mode = 0 full_duplex = 1 manual_cs = 0

Donne /dev/spidev2.0

olimex/lime_gpio.txt · Dernière modification : 2024/02/09 17:10 de 127.0.0.1